Starnberg, 24. Febr, 2017 - Geringere Latenzzeiten auf Basis neuer, nichtflüchtiger Halbleiterspeicher-Module mit NVDIMM (DRAM mit NAND Flash)...

Um was es hier geht: Flash im Bereich von Tier 1-/2 Apps und einer Vielzahl weiterer Anwendungsfälle ist dabei, die drehende mechanische Festplatte irgendwann zu ersetzen. Dies geschieht in langsamen Schritten und wird sich über einen längeren Zeitraum hinziehen, natürlich auch in Abhängigkeit von den weiteren technologischen Entwicklungen im Halbleiter-Speicherbereich. NAND Flash ist unabhängig davon aber auch gerade dabei, die Domäne DRAM-basierter Hauptspeicher (DDR4/5) zu ergänzen (Kapazität-/Kosten-/Perfomance -Aspekte).

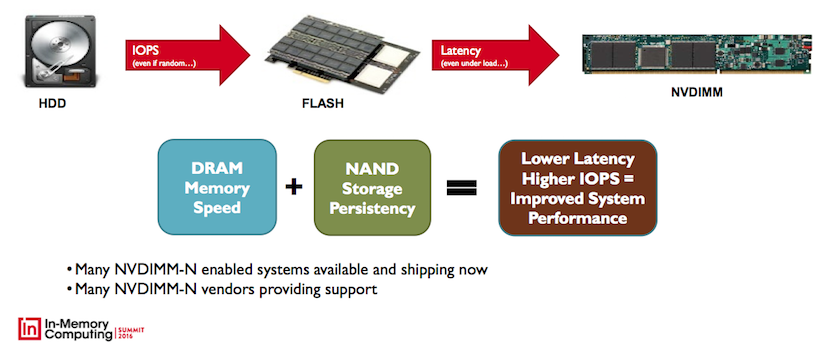

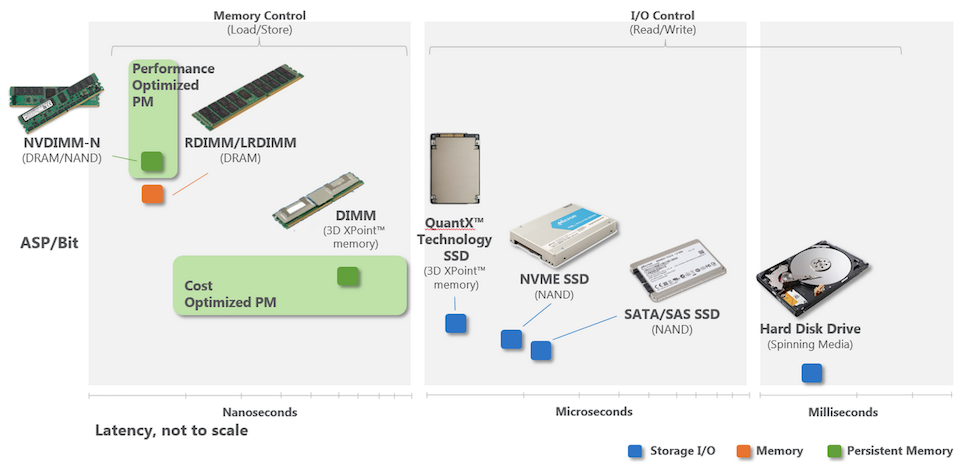

Ein Ziel dieser Entwicklungen ist es, die Geschwindigkeit von DRAM mit der Persistenz von nicht-flüchtigem Speicher bei gleichzeitig hohen Kapazitäten zu kombinieren. In diesem Zusammenhang findet der Begriff „Persistent Dynamic Random Access Memory“ Verwendung, um nicht-flüchtige, granular skalierbare und latenzarme Speicheroptionen für Server-basierende virtuelleSANs bzw. Software Definierte Infrastrukturen zur Verfügung zu stellen. Typische Hochleistungs-Serversysteme werden damit in Zukuft eine Vielzahl unterschiedlicher Low-latency Memory-Technologien als erweiterte Speicherhierarchie besitzen, die im Zusammenspiel mit Betriebssystemen und Anwendungen einen sehr granularen Ansatz des I/Os auf die Daten ermöglichen.

NVDIMM (Non-Volatile Dual Inline Memory Module) ist eine Entwicklung, die noch in diesem Jahr in breiterem Umfang auf den Markt kommen soll, nachdem erste Varianten bereits vor ca. 1.5 Jahren angekündigt wurden. Sie soll nach Meinung der Industrie (sowohl Halbleiter- als auch Systemanbieter) im Zuge der gestiegenen Anforderungen von Low-Latency-Apps nahe der CPU (memory channel) eine Rolle spielen, hauptsächlich bei virtuellen Cluster-Umgebungen, hyperkonvergenten Compute-Storage-Architekturen sowie Scale-out virtuellen Server-SANs, die mit Verbund mit neuen, aber auch bestehenden Anwendungen nach kosteneffizienten und performanten Systemarchitekturen verlangen.

Abb. 1: NVDIMM-N, Übersicht zum Aufbau (Bildquelle: US In-Memory-Computing Summit, IMC 2016)

Aktuelle NVDIMM-Varianten

NVDIMM-N: Um DRAM nicht-flüchtig zu machen (NVM) wird dem DIMM ein Flash-basiertes Backup Memory als Battery-Backup (siehe z.B. Micron „Supercap“) hinzugefügt. Bei einem Stromausfall wird der Speicherinhalt auf Flash gesichert und so dem Datenverlust im Speicher vorgebeugt. Diese Lösung - Non-Volatile Dual In-line Memory Module-N (NVDIMM-N) - genannt, verhält sich als NVRAM im Serverbetrieb wie ein DRAM-Speicher (DDR4 Memory mapped DRAM; Flash ist nicht System-mapped). Er verfügt auf dem Bord nur über eine begrenzt skalierbare Kapazität (GBs) und ist „Wort- oder byte“-adressierbar. Die Latenz von DRAM selbst liegt ja bereits im Nanosekunden-Bereich. Um den Vorteil von NVRAM bei der Byte-Adressierung für schreibintensive Anwendungen mit Betriebssystemen, Compilern etc. nutzen zu können, ist eine eigene O/S-Library notwendig, wie sie z.B. Intel / NVIDIA oder bereits Microsoft (Windows) anbieten. Aufgrund dieser Voraussetzungen kann der File I/O bei Schreibzugriffen umgangen werden, d.h. entsprechend geringer ist der I/O-Overhead. Die Verwendung von NAND im Hauptspeicher-Umfeld einer Serverumgebung macht bisherige Sytem-Overheads (Link traffic zwischen SSD, HDD und SAS PCIe - Konfigurationen) hinfällig.

NVDIMM-F: Bei der zweiten Variante, dem sog. Non-Volatile Dual In-line Memory Module-F (NVDIMM-F) besteht ein DIMM-Modul vollständig aus NAND-Zellen (Memoy mapped Flash) und stellt sich beim I/O somit nicht wie RAM, sondern als „normaler“ SSD-Block-Storage (mountable Volume via shared command buffering) dar. NVDIMM-F ist deutlich langsamer als die reine DRAM-Variante, besitzt aber durch die Verwendung von 3D NAND-Flash eine hohe Speicherkapazität (TBs). Die Latenzzeiten bewegen sich bei Flash gegenüber DRAM zwar im Microsekunden-Bereich, liegen jedoch mit NVDIMM-F damit immer noch unter denen von PCIe Flash Storage, da bei I/O-Operationen kein Datenverkehr-Overhead mit dem PCIe Controller entsteht. NVRAM mit Flash ist auf Grund des In-Memory-Betriebs auch schneller als NVMe-SSDs und damit eine zusätzliche Alternative für latenz-kritische Anwendungen. In-Memory Flash auf dieser Basis (z.B. SanDisk / Diablo Technologies) haben gegenüber NVDIMM-N den Vorteil, dass Standard-Anwendungen ohne Modifikationen oder zusätzliche Software betrieben werden können, da kein Memory- sondern Block-level Diskstorage I/O erfolgt; verbunden damit ist der geringere Preis im Vergleich zu NVDRAM. Spannend wird es auch sein, wie sich die Intel Micron 3D XPoint Technologie im Zusammenspiel mit NVDIMM positioniert: 3D X-Point - von Intel unter dem Brand „Optane“ vertrieben - ist nicht so schnell wie DRAM, aber leistungsfähiger als Flash, sodass sich dafür gute Einsatzmöglichkeiten als schneller Front-End-Cache oder auch Metadaten-Server ergeben.

NVDIMM-P: Die dritte Variante dieser NVDIMM-Technologie ist derzeit noch in Entwicklung (Vorschlag) und kann möglicherweise mit DDR5 angekündigt werden. Aus Anwendungssicht handelt sich um eine Hybrid-Lösung, also Block Storage Access via Memory mapped Flash oder über NVRAM als Memory mapped DRAM mit geringster Latenz und Byte-Adressierbarbarkeit. Damit ist die Lösung auch kompatibel mit existierenden File-Systemen und Storage Treiber (siehe NVDIMM-F). Die Kapazitäten der -P Variante sollen sich im TB-Bereich bewegen, während Latenzen im dreistelligen Nanosekunden-Bereich zu erwarten sind (Quelle: JEDEC / In-Memory-Summit US, 2016).

Fazit: Storage - oder besser die Daten - rücken auf Grund der geschilderten Entwicklungen näher an die CPU, sprich Anwendung. Gleichzeitig werden sich damit eine Reihe neuer Applikationen auch auf Basis Flash-based In-Memory-Computing realisieren lassen, die aus Kapazitäts- Leistungs- und Kostengründen deutlich flexibler im Einsatz, hochleistungsfähig und preiswerter als heutige In-Memory-Angebote sein werden. Entwickler, IT-Architekten und letztlich Anwender dürften darüber sicherlich nicht unglücklich sein...

Abb. 2: Storage Hierarchie mit Persistent Memory (Bildquelle: Micron Technologies Enterprise Storage Blog)