Yorktown Heights (NY), Starnberg, 13. Juli 2016 - IBM erzielt Durchbruch (1) bei der Skalierung von (Spin Torque) STT-MRAM durch Perpendicular Magnetized Materials...

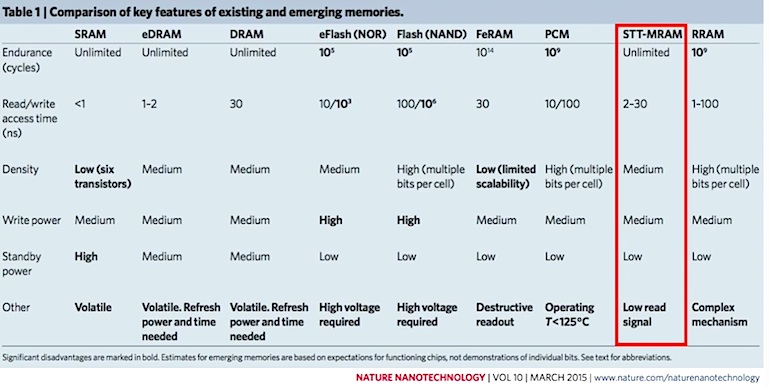

Zum Hintergrund: Aktuell dominieren HDDs, DRAM und FLASH die (online-) Server- und Speicherwelt. Über eine Entwicklung wird hingegen relativ wenig gesprochen: STT-MRAM, nichtflüchtiges /non-volatile Magneto-resistive random-access memory ist im Gegensatz zu Flash deutlich schneller und langlebiger (unbegrenzte read-/write cycles!, klein (11 nm), green memory, fast so schnell wie SDRAM...) und könnte laut aktuellem Forschungsstand (IBM-Samsung Kooperation bei Spin Torque MRAM) künftig eine interessante Alternative als universeller Halbleiterspeicher zu NAND-Flash oder DRAM Storage darstellen. STT-MRAM im Vergleich zu Flash ist laut IBM (siehe Quellen und Abb. 1 unten) auf Grund des Forschungs-Durchbruchs bei der Materialauswahl (perpendicular magnetized) leichter herzustellen, dabei sehr robust, besitzt eine extrem niedrige write-error rate, WER (siehe Quelle 1 unten) bei gleichzeitig hoher Energieeffizienz.

Mögliche Einsatzgebiete von STT-MRAM auf Grund dieser Eigenschaften sind High-Performance-Server (Data Caching), IoT Sensor-Geräte oder auch intelligente personal Mobile Devices für den Consumermarkt. Zitat aus wikipedia.org: „MRAM has similar performance to SRAM, similar density to DRAM but much lower power consumption than DRAM, and is much faster and suffers no degradation over time in comparison to flash memory. It is this combination of features that some suggest makes it the “universal memory”, able to replace SRAM, DRAM, EEPROM, and flash. This also explains the huge amount of research being carried out into developing it.“

(1) Quelle: Voltage and size dependence on write-error-rates in STT

- MRAM down to 11 nm junction size. J. J. Nowak, R. P. Robertazzi, J. Z. Sun, G. Hu, J. H. Park, J. H. Lee, A. J Annunziata, G. P. Lauer, C.Kothandaraman, E. J. O'Sullivan, P. L. Trouilloud, Y. Kim, D. C. Worledge

- IBM-Samsung MRAM Alliance, IBM TJ Watson Research Center, Yorktown Heights, New York

Zitat aus der Einleitung: "Abstract—The dependence of the write-error-rate (WER) on the applied write voltage, write pulse width, and device size was examined in individual devices of a Spin Transfer Torque MRAM 4 kbit chip. We present 10 ns switching data at the 10-6 error level for 655 devices, ranging in diameter from 50 nm to 11 nm, to make a statistically significant demonstration that a specific magnetic tunnel junction stack with perpendicular magnetic anisotropy is capable of delivering good write performance in junction diameters range from 50nm – 11 nm. Furthermore, write-error-rate data on one 11 nm device down to an error rate of 7*10-10 was demonstrated at 10 ns with a write current of 7.5 uA, corresponding to record low switching energy below 100 fJ."

Die gesamte vorliegende wissenschaftliche Publikation (vier Seiten) für das IEEE finden Sie hier als PDF-Dokument (s.a. Anhang unten) zum freien Download!

Weitere Quellenangaben zur IBM-Forschung mit fachlichen Links:

Researchers celebrate 20th anniversary of IBM’s invention of Spin Torque MRAM by demonstrating scalability for the next decade

Hinweis auf Research-Konferenz: "on November 7, 2016 IBM is hosting a special 20th Anniversary Spin Torque MRAM Symposium at the Thomas J. Watson Research Center in Yorktown Heights, New York. The one day event will feature a series of talks including keynotes by Slonczewski and other leading scientists from around the world." > Link zu IBM Research mit Agenda und weiteren Details...

Abb. 1: Bildquelle IBM Videozitat aus Nature Nanotechnology, Vol 10, March 2015, Comparison of existing and emerging memories..