Seoul (Korea), Starnberg, 30. Juni 2017 - 64-Layer 256-gigabit (Gb) 3-bit Multi-Level-Cell (MLC) V-NAND-Chips als technologische Basis für das Terabyte V-NAND-Zeitalter…

Zum Hintergrund: Samsung Electronics Co. Ltd. hat mit der Massenproduktion von 256Gb V-NAND Flash Memory mit 64 Lagen für die Nutzung mit einem erweiterten Angebot an Speicherlösungen (Server, PC und Mobilgeräte-Applikationen) begonnen. Der Hersteller beabsichtigt nach eigenen Angaben für die Massenproduktion des 64-Layer V-NAND Chips - vielfach als V-NAND der vierten Generation bezeichnet - mehr als 50 Prozent seiner monatlichen NAND-Flash-Produktion bis Jahresende abzudecken. Das 3-bit-256Gb-V-NAND mit 64-Layern bietet eine Datenübertragungsrate von 1Gbit/s und ist laut Anbieter damit der schnellste derzeit verfügbare NAND-Flash-Speicher.

Darüber hinaus erreicht V-NAND von allen NAND-Flash-Speichern die kürzeste Page Program Time (tPROG) von 500㎲ ** - dies ist etwa vier Mal kürzer als bei typischem Planar NAND Flash Memory mit 10-nm-Strukturen und etwa 1,5 Mal schneller als Samsungs schnellstes 3-bit-256Gb-V-NAND-Flash Memory mit 48-Layern. Es wird nach Expertenmeinung erwartet, dass sich die Hersteller nun stärker auf die Leistungsfähigkeit und Zuverlässigkeit bei Memory-Storage fokussieren, als auf den Wettlauf bei der Chip-Skalierung.

Das neue 64-Layer 256Gb V-NAND bietet über 30 Prozent Produktivitätsgewinn gegenüber seinem Vorgänger, dem 256Gb V-NAND mit 48-Layern. Darüber hinaus wird das 64-Layer V-NAND mit 2,5V versorgt, was zu einer etwa 30 Prozent höheren Energieeffizienz gegenüber den 3,3V, die das 48-Layer V-NAND nutzte, führt. Auch die Zuverlässigkeit der neuen V-NAND-Zelle soll sich danach gegenüber seinem Vorgänger um etwa 20 Prozent erhöht haben. Samsung erreicht diese Verbesserungen durch Konzentration auf unterschiedliche Herausforderungen, die sich in dem fortschrittlichen V-NAND-Fertigungsprozess stellen. Zu den größten Herausforderungen gehört die Herstellung mehrerer Milliarden Kanallöcher, die mehrere Dutzend Layer von Zell-Arrays durchdringen und den Verlust von Elektronen von rund 85,3 Milliarden Zellen minimieren.

Da sich die Zahl der Layer von Cell Arrays erhöht, steigt auch der technologische Schwierigkeitsgrad. Dies gilt speziell für die Aufgabe, die Kanallöcher homogen in ihrer Form vom oberen zum unteren Layer zu machen und für die richtige Verteilung des Gewichts aller Layer zur Verbesserung der Stabilität der Kanallöcher.

Eine weitere Herausforderung, die Samsung gemeistert hat, bestand darin, 64 Lagen von Cell Arrays auf der Basis von 3D CTF (Charge Trap Flash) Struktur zu realisieren und auf die innere Seite jedes Kanals eine atomisch dünne nichtleitende Substanz gleichmäßig aufzubringen. Dies führte zur Realisierung von kleineren Zellen mit höherer Leistungsfähigkeit und Zuverlässigkeit.

Aufbauend auf 15 Jahren Forschungsarbeit an seiner proprietären V-NAND-3D-Struktur, hat Samsung (Semiconductor) nach vorliegenden Informationen die Grundlage für über 500 Patente über wesentliche technologische Erkenntnisse geschaffen und diese in vielen Ländern, darunter Korea, USA und Japan, beantragt. Damit ist die Technologie vorhanden, die das Unternehmen in Zukunft braucht, um V-NAND-Chips mit Speicherkapazitäten von einem Terabit und mehr zu produzieren, indem es über 90 Lagen mit Cell Arrays stapelt.

** Page Program Time (tPROG) ist die Zeitperiode, die benötigt wird, um Daten auf einer bestimmten Zelle aufzuzeichnen. Es ist ein Schlüsselparameter, der die Schreib-Leistungsfähigkeit eines 64-Layer-V-NAND bestimmt.

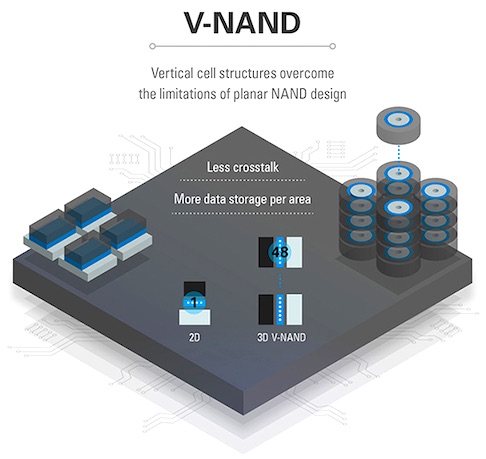

Abb. 1: Samsung V-NAND Übersicht (Bildquelle Samsung Electronics Co. Ltd.)